In each article on Habré, dedicated to domestic microprocessors, one way or another, the issue of licensed IP blocks is raised and how much their presence and absence reduces the value, domesticity or safety of development. At the same time, many commentators do not understand the subject of discussion too well, so let's try to understand how exactly the licensing in the microelectronic industry works, what is good and what is wrong with licensed units, and what is the chip design process if most of the blocks in it are purchased.

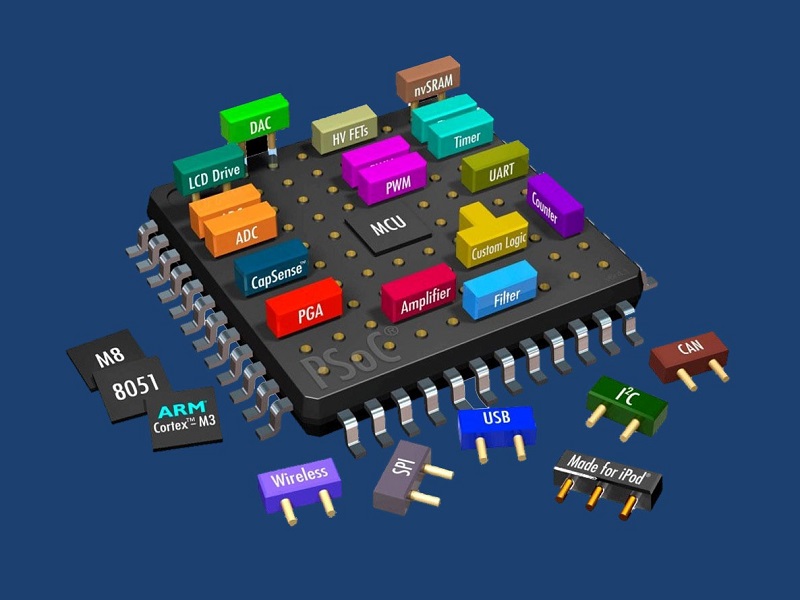

Any modern microcircuit is what some time ago it was proudly called “system on a chip”: even three-legged linear regulators and sources of reference voltage have a digital adjustment hidden from the user, let alone microprocessors and microcontrollers containing dozens of different blocks, the development of each of which requires specific skills and great experience to circumvent the pitfalls that are not written in books and articles. At the same time, any project, as a rule, has its own killer feature, due to which developers expect to gain an advantage over competitors, and this particular killer feature should be done as well as possible, and all other blocks should be just as good as the others.

Attention, the question is: do you need to have an expensive development team capable of making all the necessary blocks yourself?

Even more interesting question: if you yourself have developed a microprocessor command system, do you need to have a team of programmers who

will write a compiler for it , port the latest kernels of popular operating systems, do a lot of other hard work and most likely still don’t put your creation on a level with popular architectures that many more people work on?

And most importantly: will positive answers to the previous two questions give competitive advantages to your product?

Lyrical digressionOn June 5, Morris Chang retired — a man you had never heard of, but without which there would be no modern electronics. Born in China, Morris Chang left for the United States at the height of the civil war, graduated from MIT, and then worked for Texas Instruments and General Instruments for many years. In those years, an integral part of any microelectronic company was its own production, the equipment for which cost several orders of magnitude cheaper than it is now, but nevertheless, it was still very expensive. Here is how Chang himself wrote about it:

It was not making it easy to move on. to form their own company. It was a thought that every company needed a manufacturing company, an IC company. It was a fab.

In 1985, Morris Chung was about to retire, but instead accepted an offer from the government of Taiwan to work at the Industrial Technology Research Institute, a research institute that was supposed to help make an industrial revolution in Taiwan and eliminate the backlog of the economy from developed countries. In 1987, in parallel with working at ITRI, Chang created TSMC, a company that grew into the world's largest manufacturer of integrated circuits. The TSMC business model was originally built on the fact that the company does not develop anything, but only produces foreign developments, and this was one of the first steps in creating a modern ecosystem of developing and producing microcircuits, known as the Fabless model.

End of lyrical digressionWhat is Fabless?

Fabless is a model for the development and production of microchips, in which the development company does not have its own production and uses the services of a third-party factory, which also cooperates with other developers (and sometimes has its own products).

The presence of third-party factories makes it possible to radically reduce the threshold for entering the microelectronics market (which Morris Chang dreamed of at one time) from hundreds to millions of dollars due to the absence of the need to buy and maintain production equipment. It also allows to reduce this threshold even further due to the formation of the market for suppliers of complex functional units (they are Silicon IP). If you produce chips in your own factory, then you can only rely on your own strength and must contain a team capable of creating all the necessary blocks. If the factory is used not only by you, but also by other companies, then most of the typical tasks have already been solved by someone, and you can use the results of the labor of others - or resell your own solution to someone else, having previously agreed on the price and conditions so that no one was left behind. Of course, you are unlikely to sell your know-how to direct competitors, but there are plenty of situations where you can earn money without getting involved in a conflict of interest. It was out of the possibility and desire to reuse the results of solving typical tasks that the IP-block market emerged, the size of which, as of 2017, was close to four billion dollars and continues to grow rapidly.

What is profitable?

Buyer IP - first and foremost savings. According to various estimates, the purchase of IP-blocks usually turns out to be two to five times cheaper than self-development. In addition, the purchase usually allows you to significantly reduce development time, since you do not need to independently produce test chips and correct errors.

An IP developer is able to build a working business on a niche solution and significantly reduce the cost of doing business. The cost of the microcircuit includes a significant part of the cost of marketing, packaging, testing, technical support, application software, and finally, photomasks for mass production, etc. etc. If you do not produce finished products, but only sell blocks, then you do not have all these expenses.

Factory - an opportunity to attract more customers. Large factories tend to create around them an ecosystem of suppliers of IP-blocks, because their use can significantly speed up the design and, equally important, automate it as much as possible. A rich portfolio of ready-made components is a great help in the design of the final product, because it allows you to do yourself only what your know-how is and not to waste precious resources on developing everything in general - especially in a situation where there is already a ready-made solution developed by people. who have invested significantly more time and experience in its development than you can afford. Accordingly, a wide selection of ready-made IPs can be a serious factor in choosing a factory for the production of your project.

How it works?

Let's look at the licensing of nuclei on the example of a spherical customized system on a chip. The system will contain a processor core, buses for combining the core and peripherals, a certain amount of cache memory, interfaces for communicating with the outside world (say, CAN and I2C), PLL, DAC and ADC. For the purity of the experiment, let us assume that everything will be bought at all, without independent development. “Stupid assumption,” you say, and you’re not quite right. In reality, of course, such situations are extremely rare, but nevertheless it is quite possible to imagine that the killer feature of the product will not be some kind of unit by itself, but a specific combination of already existing units. For example, you are the first buyer of the block (therefore, the competitors do not yet have it) or have invented an application in the uncharacteristic segment for the existing block (therefore, the competitors in this segment have nothing similar).

So let's start with ...

... no, not from the processor core, but from the analog strapping. For example, take the analog-to-digital converter (ADC) - a typical unit of most microcontrollers and any other systems dealing with data from the outside world.

An ADC is an analog block, which means its parameters seriously depend not only on its circuitry, but also on how this circuitry is implemented on a chip. If we take the finished file with the topology from one process and produce it at another factory with the same design standards, we can get completely different parameters (not to mention the transfer to other design standards). However, the culture of “second suppliers” known from the middle of the century still exists; for example, the Towerjazz factory offers copies of some TSMC process technology.

The ADC is a great example of a Hard IP block tied to a specific process. In order to buy such a unit, you must know exactly what technology your final product will be manufactured on, and, as mentioned above, having the Hard IP you need can be a serious competitive advantage for the factory.

In what form is Hard IP delivered? This is an interesting question, and to answer it, it is necessary to discuss in what form such a block is being developed. In the case of most analog blocks, the development of circuitry is carried out at the level of individual transistors, that is, the output files will be a circuit file and a file with topology. At the same time, features and schemes, and topologies can have serious commercial value, which, of course, I don’t want to outsource. And in order for the client to not be able to reverse-engineer the circuit by topology, the topology is usually not transmitted either, so in the usual case the supplied files look like this:

- Instead of the wiring diagram, the client receives a high-level behavioral model that does not reveal the features of the implementation. Such a model can be written in Verilog-A. Alternatively, some CAD systems (for example, Cadence Virtuoso) support encryption of electrical circuits, that is, the client will be able to use your circuit (or the verilog-A file), but will not be able to open and view the contents.

- Dimensional layout of the topology, with marked external findings and a description of how many levels of metallization is occupied by the block.

- Test environment for verification of basic parameters.

- Documentation.

In this case, of course, it is necessary to involve a third party, to whom you can transfer the topology, without fear of competition and reverse engineering. This third party is the factory, and its intermediary role between customers and performers is an important part of the chip development ecosystem. The factory, of course, should have a crystal clear reputation (this is about the bookmarks) and, ideally, it should not produce anything like it on its own, because working in a competitor’s factory is in any case a dubious pleasure. Samsung turns out to produce processors at the same time and Apple itself, but other large factories usually either concentrate on their own production (like Intel), or completely abandon their own development (like TSMC). The desire to get rid of this conflict of interests, by the way, was one of the drivers for the selection of Globalfoundries (the second largest player in the factory market) from AMD.

Lyrical digressionBy the way, there are no pure-play factories in Russia. Moreover, for absolutely all market players, the production of their own products is a priority, and all domestic circuits produced by fabless developers are made at the facilities of their potential competitors - or at pure-play factories abroad.

End of lyrical digressionThen there is another important detail of the interaction between the supplier and the factory: the factory puts your IP block into its own database and further checks all incoming projects for the presence of your topology (which someone could get from you as well as illegally), and It consults with you as to whether the requester has a production license (as many cheap licenses imply the use of a block in only one project). Availability of verification by the factory allows the Hard IP developer to choose any convenient licensing option - tied to the number of projects, the number of chips sold, the timing of the launch of chips into production, etc. etc. But more about the types of licenses - in the next section.

As a Hard IP in a typical on-chip system, ADCs, PLLs, and physical I / O interface layers will be needed.

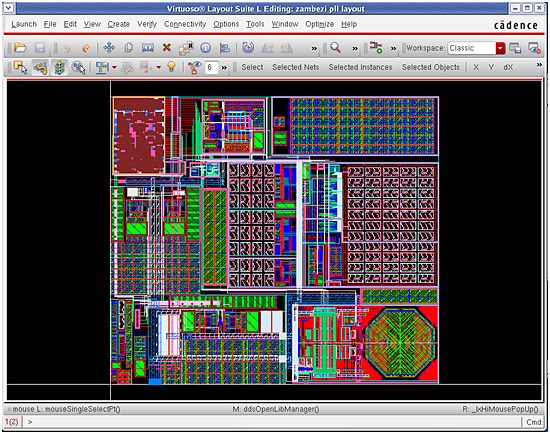

Cadence Virtuoso Layout Suite CAD window with analog Hard IP block topology (this is PLL, if anyone is interested). The borders between the individual subblocks (which are usually made by different people) are clearly visible and, for example, a very rare element for integrated circuits - an inductor in the lower right corner. And at the top left you can see a digital block (probably, control) and its multi-bit interface to the rest.

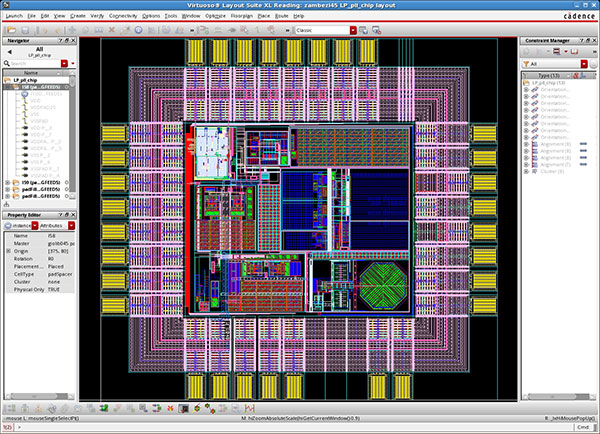

It is the same, but in the form of a finished chip (for example, for testing). The I / O pads and rings connecting them from lands and feeds are clearly visible.

The term "Hard IP" is also used to refer to IP blocks for FPGA. In this case, it is assumed that the block code has been optimized for use in a particular FPGA model and synthesized for placement in it.

Soft ip

The next block we will look at is the processor core. Actually, almost any digital circuit can be in its place, for example, a signal encoding unit with a Reed-Solomon code, but the processor cores are most popular and they make up a good half of the entire market (including due to complexity and high prices).

The main difference between developing digital circuits and developing analog circuits is that digital circuits are usually written in special high-level languages — Verilog or VHDL, and then a special CAD system synthesizes the electrical circuit and topology from this code. So, until the synthesis, the code is not tied to a specific technology, and the same block can be produced at different factories (or sewn into an FPGA) or at different versions of the same technology (for example, optimized for high speed or low power consumption) . This, in fact, is used by development companies, such as, for example, ARM. Such digital blocks that are not tied to a specific technology are called Soft IP.

Here is the scheme of one bit adder:

And this is how an eight-bit adder actually looks in the design of a microcircuit:

module adder(

input wire [7:0]a,

input wire [7:0]b,

output wire [7:0]out,

output wire carry

);

assign {carry, out} = a + b;

endmodule

, , , . , IP- .

Soft IP? :

• Clean, readable, synthesizable Verilog HDL, VHDL

• Cadence Encounter RTL Compiler synthesis scripts

• Documentation – integration and user guide, release notes

• Sample verification testbench

Encrypted source along with a complete certification data package (CDP) including all artifacts required for chip-level compliance.

, — , ( IP ). , . , - -, , .

, LEON3:

- , Cobham Gaisler, LEON3 GPL

- LEON3FT ( ): The LEON3FT core is distributed together with a special FT version of the GRLIP IP library, distributed as encrypted RTL.

- ( ) , LEON2FT, .

, , Verilog-, . Verilog- , , , , . digital watermarks, , IP.

, “Clean, readable, synthesizable” , , IP . , , , ( , hardware trojans) , , , .

, : soft IP , , ? , Soft IP, , .. .… :

ARM, , , , , ( ), IP , - , , . . (, , , ). Apple Imagination Technology in-house , Apple , Imagination ( ).

, — ( IP ) ( ).

soft IP FPGA, , . , Xilinx IP, ( ) , , ( , ).

, , .

— IP- . , -, . , IP, , IP , , IP ( , ); , - .

— . , ( IP).

— . , , , . — . , , .

— , , (, ARM Cortex). — , .

— . (, , ) , — ( , , ). ? , ( - , , ) . , , , , , — .

? : , , , . , Apple, ARM - , , (, ARM ) — .

: , , , , , , ( — ). , , . , , Apple, , , ! ARM, , Apple . , ARM . , , Apple — PowerPC, , PowerPC x86, Apple Intel.

Soft IP , - , IP . :

- , “ — ”, .

- - IP ( ), IP, IP ( IP hardening) . ? , , , .

soft IP ( ), , , .. ..

Configurable IP

IP, hard soft — , . - , - . ? , IP-? ?

( , FPGA) , , , . , , IP- Hard IP, Soft IP ( , ).

— -.

Foundation IP

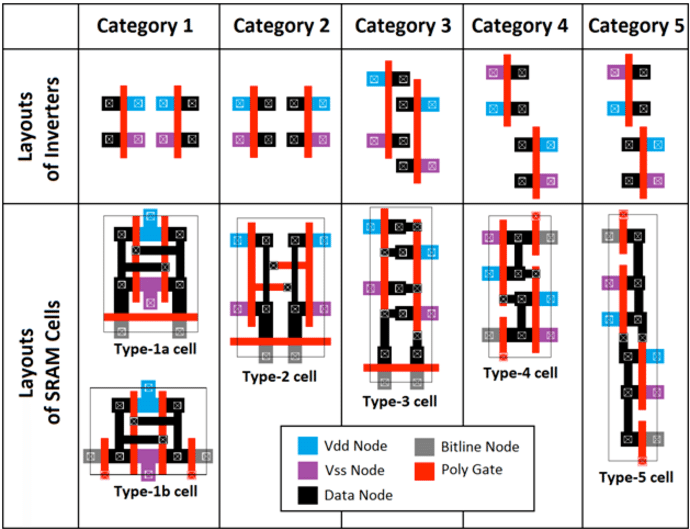

«-hard» IP- — foundation IP, . — , . , , , , , . , , ( ) , (, ) . «generic» , , , , , .

Foundation IP -, , , .

BarsMonster .

Verification IP

, , — , . , , , . , , . , - . “”. .

, — Verification IP. — , , ( ). Synopsys , , Synopsys — IP-. IP Design&Reuse Synopsys 828 Silicon IP ( ARC — ARM) 116 Verification IP .

verification IP CAN, ( APB AHB ARM) - . , , , .

?

, , , , ? .

:

- , ( verification IP ).

- — .

- ( , ).

- Soft IP , .

- , , .

- , , .

- , .

- , ( ).

, , ( ). , - , « - BGA 400-700 ». , Hard IP- 400-700 , , , 4-8 (, Soft IP). — ? , . , «-» .

— Synopsys IC Compiler , .

, — , , , , , , .

, , fabless- IP- , , , . , , ( “”) , , : , , , , , , - . , , — .

: Open Source?/ Open Source . , - ( ) , - . , , - . , , .

—

Opencores.org, — OpenRISC, ( FPGA), ASIC ( Samsung). Opencores, , - , ( ARM), FPGA. FPGA Proven, — ASIC Proven.

—

RISC-V. ( OpenPOWER OpenSPARC) , - , , ( ).

RISC-V — , MIPS, , , , ( , MIPS). RISC-V Foundation Google, Samsung, NXP, NVIDIA . , , , , OpenPOWER, , , ARM , ARM, , , ( Intel). - . RISC-V (

RISC-V), - , . , ,

RISC-V — Falcon NVIDIA.

: ?OpenCores, IP- ( ) . :

TSMC IP Alliance, IP .

Design&Reuse, IP-, ( ).

ChipEstimate, D&R, .

— ?, , , - .

— “” (), “” ( ), “” “” (211), “Neuromatrix” ( “”), RISC-V (Syntacore), ARM, MIPS, SPARC, MCS96, MCS51, C166, AVR, MSP430.

,

“ ” ( ):

IP-:

: ARM Cortex-M4F, ARM Cortex-M0, ARM946E-S c AMBA, ARM VFP9-S, SPARC v.8 c AMBA. 8- RISC .

IP- (PLL) TSMC, KeyASIC AnalogBits, Sidense Memory, - (eFuse) TSMC, IP- , ROM RAM ..

“ ” , IP- - (-, IP-).

IP? IP- (

“ ”,

“”,

211), . Design&Reuse ChipEstimate “ ” ( ) NTLab. , .